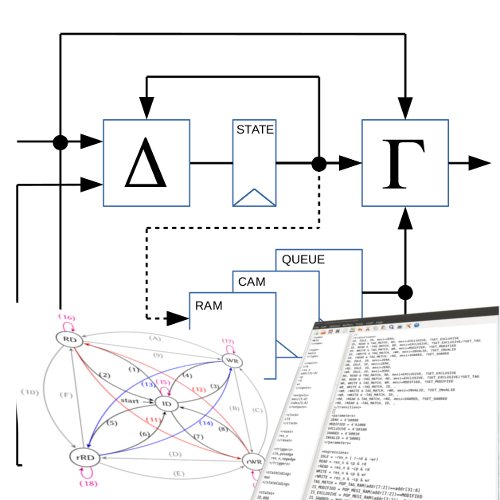

"Universal Memory Automata (UMA) are founded on the theory of Deterministic Finite Automata. UMAs extend the concept of Push-Down Automata with a user defined number of other memory structures to benefit from advanced access paradigms."

"The RAPID VHDL package is in an initial state and intended to speed-up the HDL design phase. The package provides parametrized synthesizable VHDL code for basic digital structures."

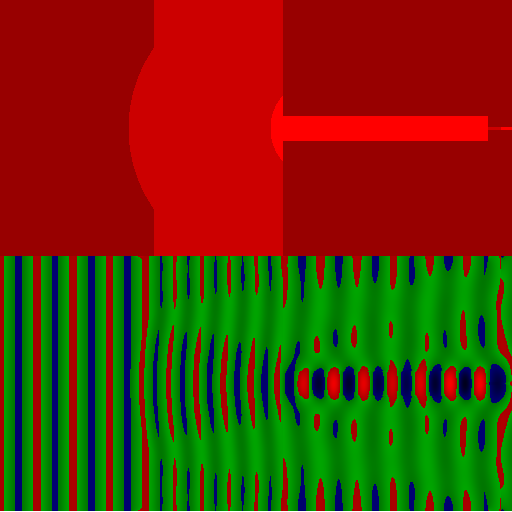

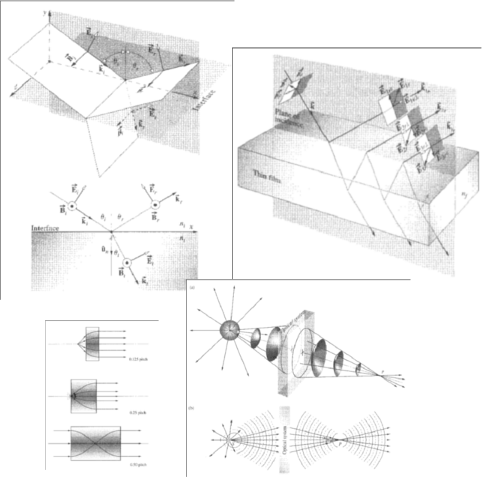

"Massively Parallel (MP) systems help to speed-up electromagnetic simulators. The work is focused on the optimization of 2D and 3D Fourier methods like the WPM and the VWPM."

"The WPM and VWPM are Fourier methods applicable to high-order spatial frequencies. The bidirectional forms of the WPM and VWPM allow simulations of Bragg resonators and comparable systems."

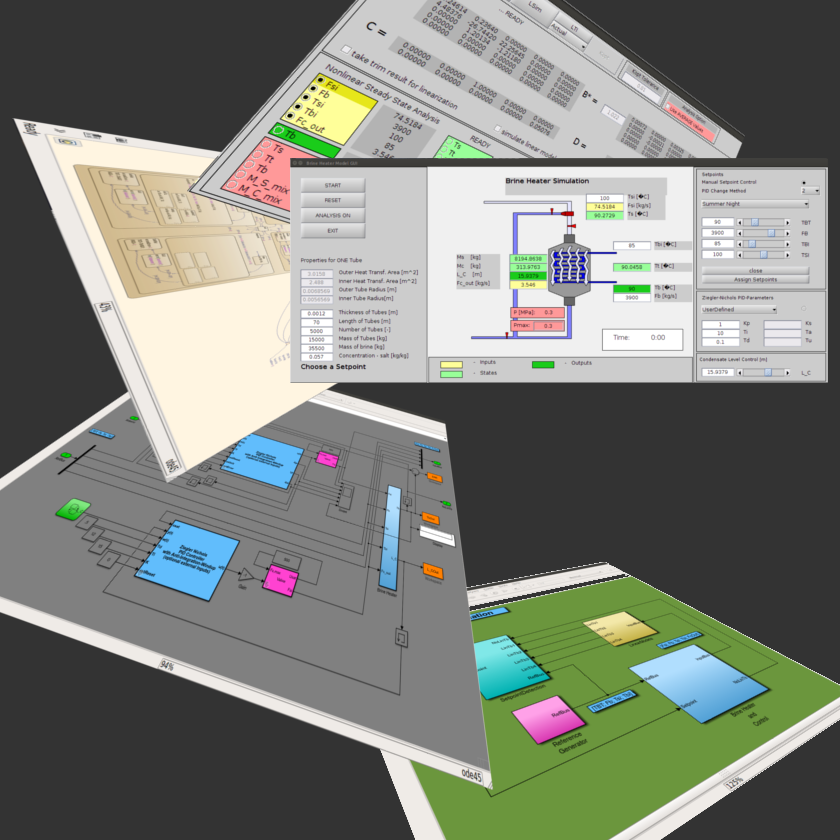

"Hybrid modelling and control for a Brine Heater of a Multi-Stage-Flash desalination plant implemented with Matlab."

(BSc)

(BSc)

(BSc)

(BSc/MSc)

(BSc/MSc)

(MSc)

(BSc/MSc)

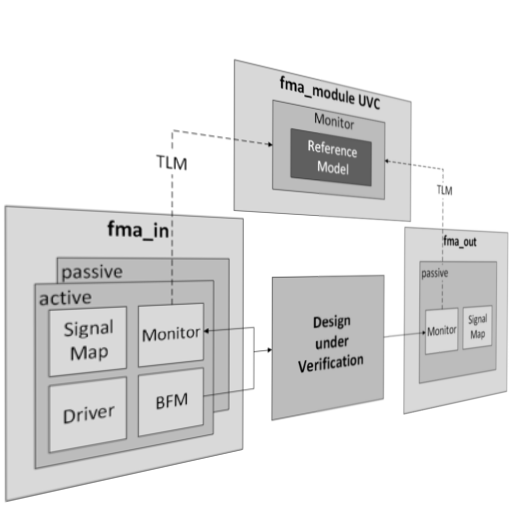

"A former master thesis [w3] and todays test vehicle for verification exercises."

A free Instruction Set Architecture (ISA) invented by the UC Berkeley. RISC-V is one of the example architectures in the microprocessor architecture course [w3]

(MSc)

(MSc)

(MSc)

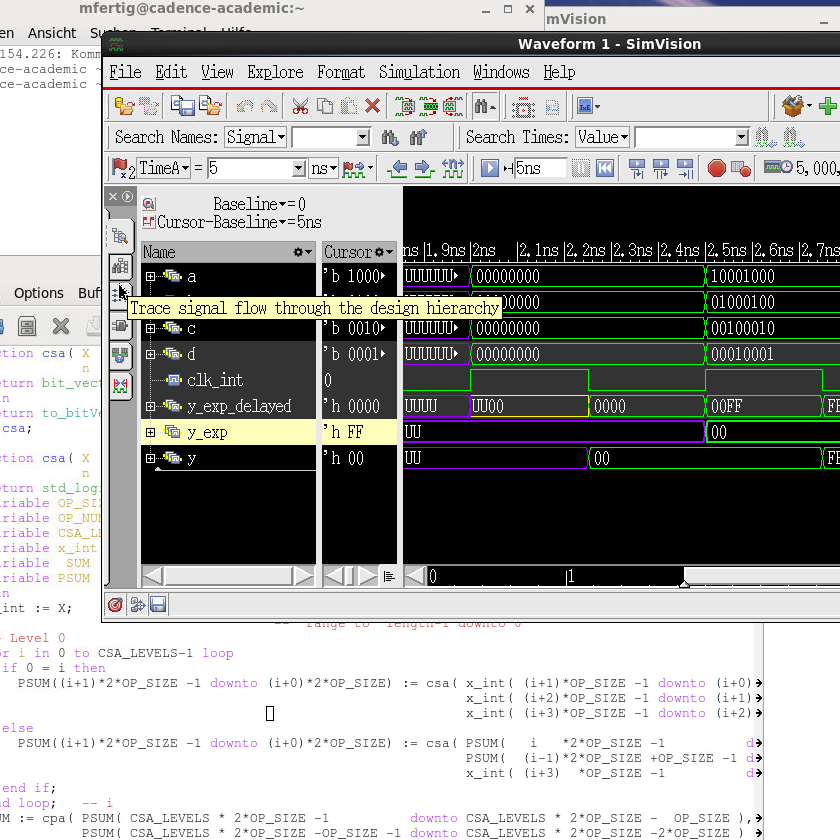

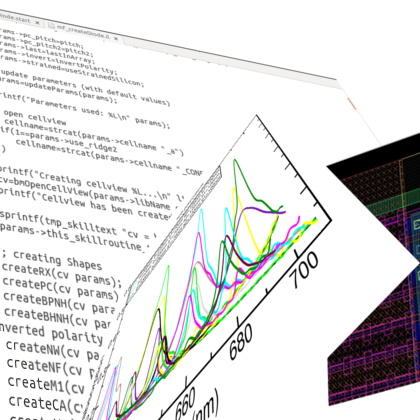

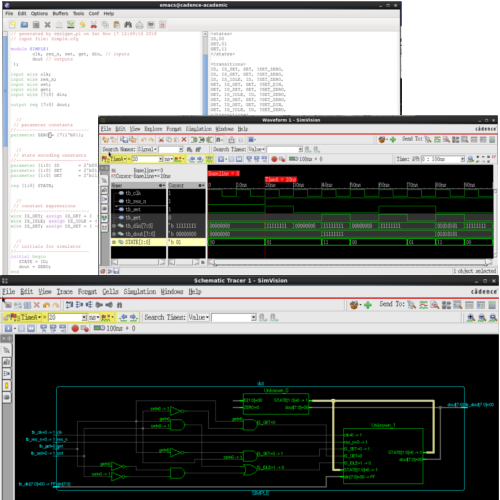

As an academic organization and user of a Cadence academic license agreement, we hereby make our work visible.

The ASIC design environment is used for educational purposes in lectures and student laboratories. Digital ASIC design is performed with the Cadence framework.

Students are trained on the front end design flow including HDL design (VHDL or Verilog), simulation, verification, synthesis and static timing analysis as well as the basic back end design flow.

The environment is used in the courses 'Digital ASIC Design Tools Lab', 'SystemVerilog for Design' and 'SystemVerilog for Verification'.

Power Management ICs …

Compact Wheel Loaders …

Microprocessor design …